作为一名资深工程师,我在内存时序方面积累了丰富的经验,今天我将分享给大家,希望能对大家的工作和学习有所帮助。本文主要从三个方面进行详细讲解。

一、时序设计要充分考虑信号传输时间

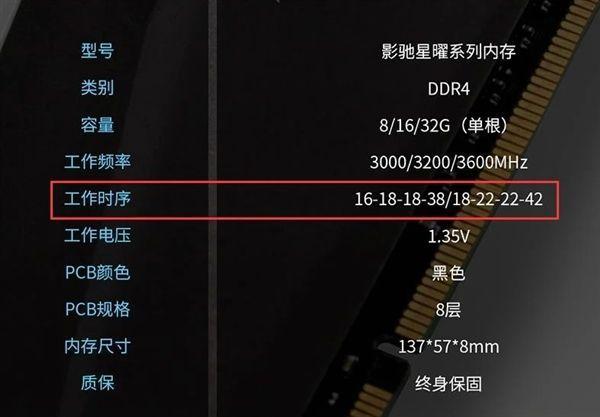

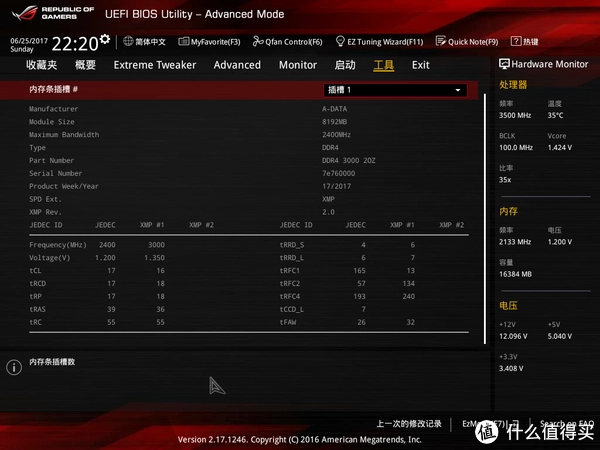

在内存时序设计中,信号传输时间是一个非常重要的因素。我们需要仔细计算信号从发出到到达目标设备所需要的时间,并根据这个时间来调整时序。为了保证稳定性和可靠性,我们需要留出足够的时间来确保信号能够完全传输到目标设备上。

在实际设计中,我常常会遇到一些信号延迟过长或者延迟过短的问题。为了解决这些问题,我会通过不断调整时序参数,并通过仿真和验证来确保信号能够准确传输。通过这样的经验总结,我逐渐掌握了如何在时序设计中充分考虑信号传输时间的方法。

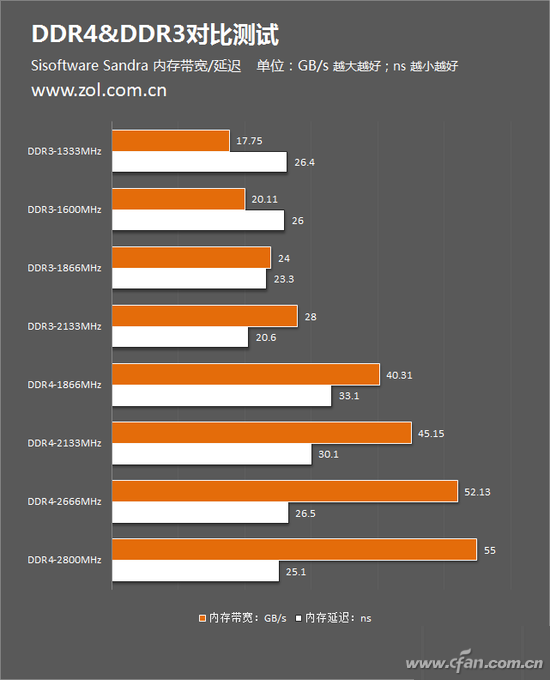

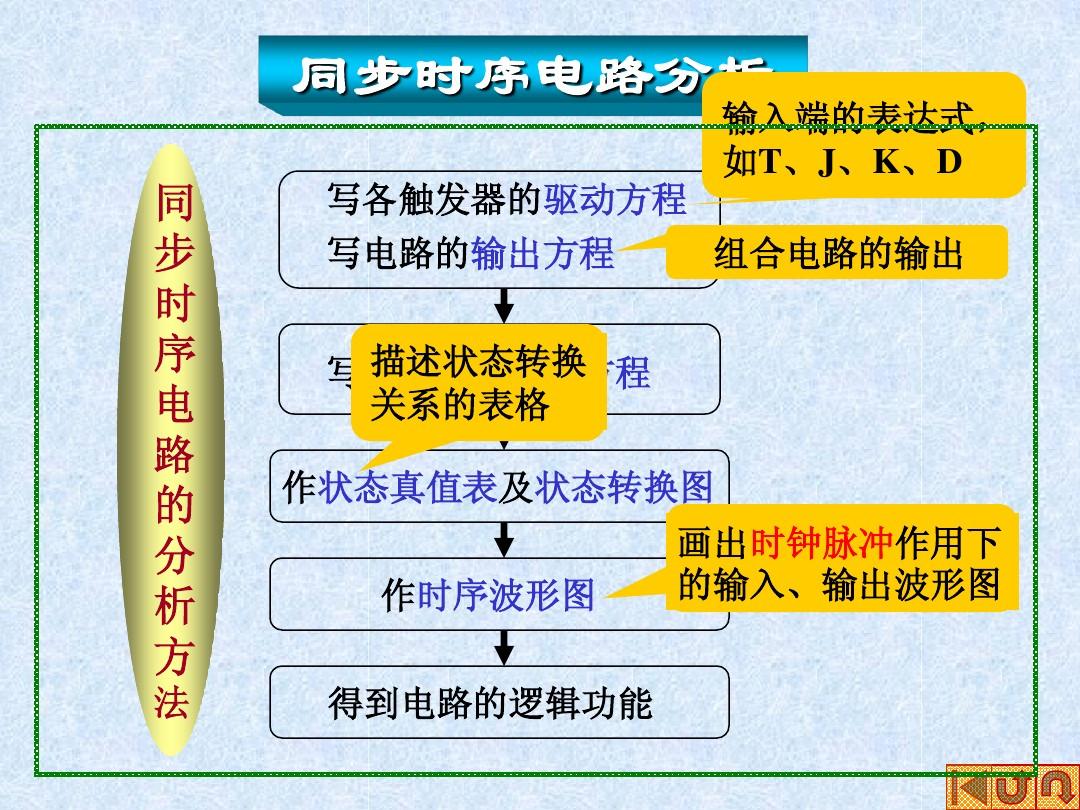

二、合理设置时钟和触发条件

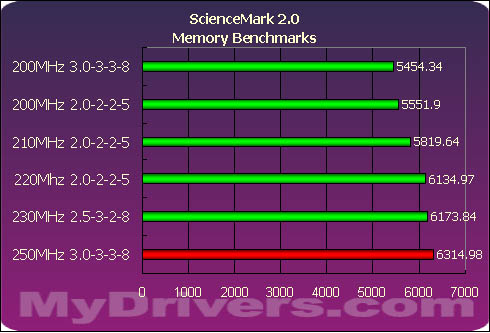

在内存时序设计中,时钟和触发条件的设置是非常关键的。合理设置时钟频率和触发条件可以保证内存的正常工作,提高系统性能。我在实践中遇到过一些时钟频率过高导致内存无法正常工作的情况,通过调整时钟频率和触发条件,我成功解决了这个问题。