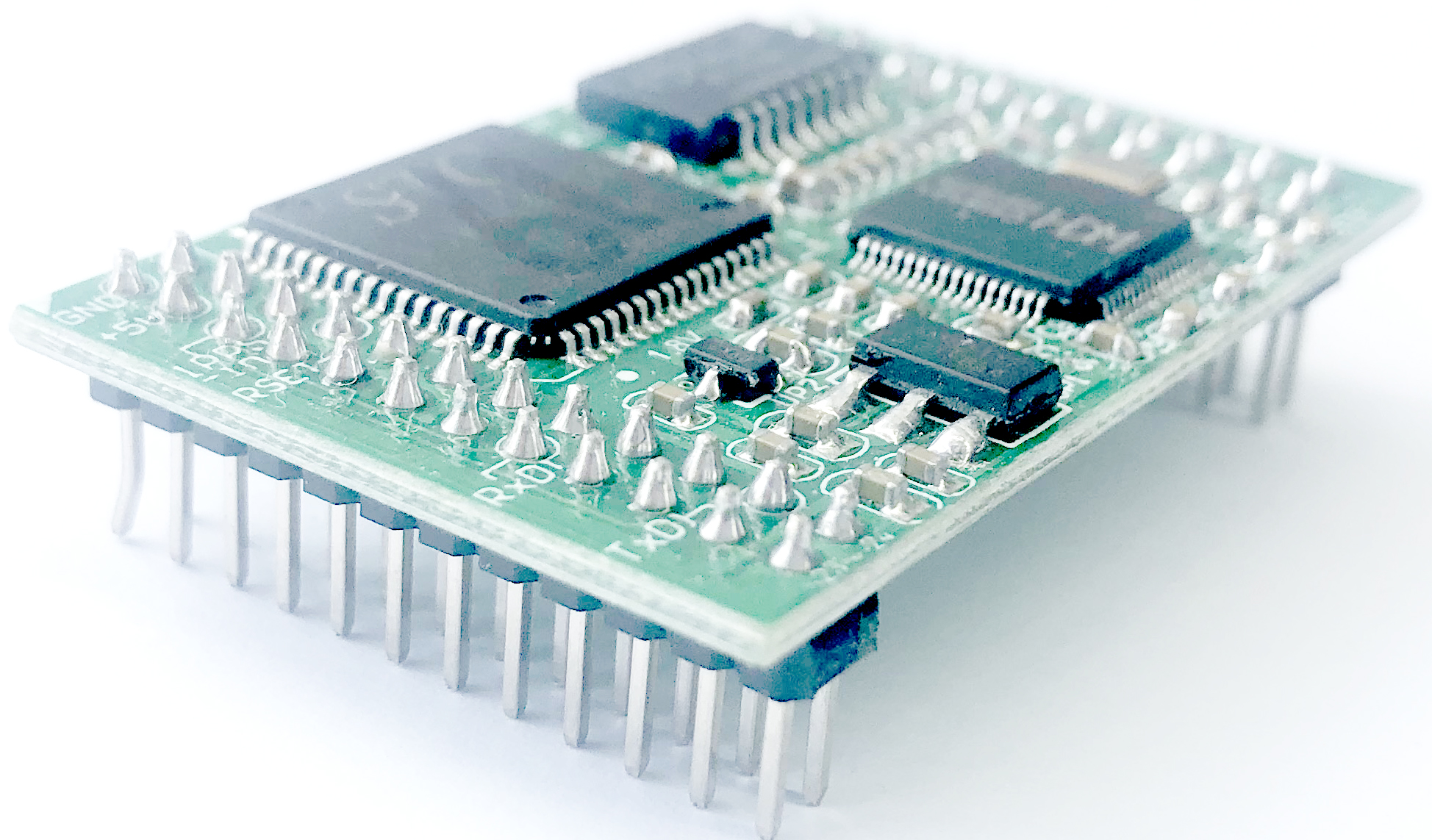

高频内存时序是我们在设计电路板的过程中经常会遇到的一个挑战。在这篇文章中,我将分享一些我在处理高频内存时序时的经验和技巧。希望这些经验对你们有所帮助。

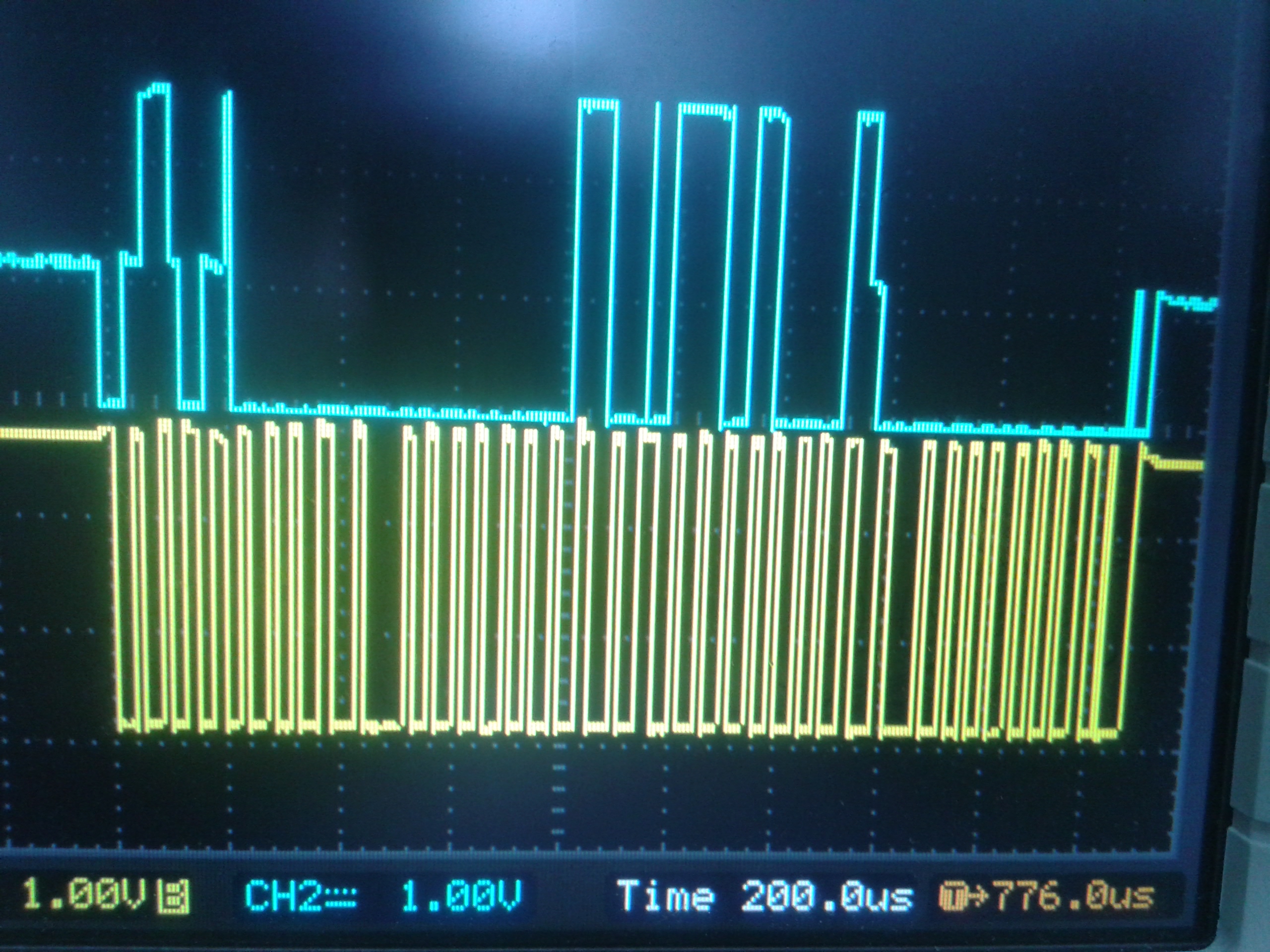

1.时钟边沿的选择

在处理高频内存时序时,选择合适的时钟边沿非常重要。不同的时钟边沿会对信号传输和稳定性产生不同的影响。我通常会选择上升沿作为时钟边沿,因为上升沿可以提供更好的信号延迟和稳定性。当然,在具体设计中还需要考虑其他因素,比如功耗和布线复杂度等。

2.信号路径优化

在高频内存时序中,信号路径的优化至关重要。合理规划信号传输路径可以减少信号干扰和延迟,提高系统性能。我通常会采用以下几个方法来优化信号路径:

-最短路径规划:尽量减少信号传输路径的长度,以降低延迟。

-信号层次分离:将不同类型的信号分离到不同的信号层次,以减少信号干扰。

-电源和地线规划:合理规划电源和地线的布局,以降低噪声干扰。

3.时序校准和调整